本記事の概要

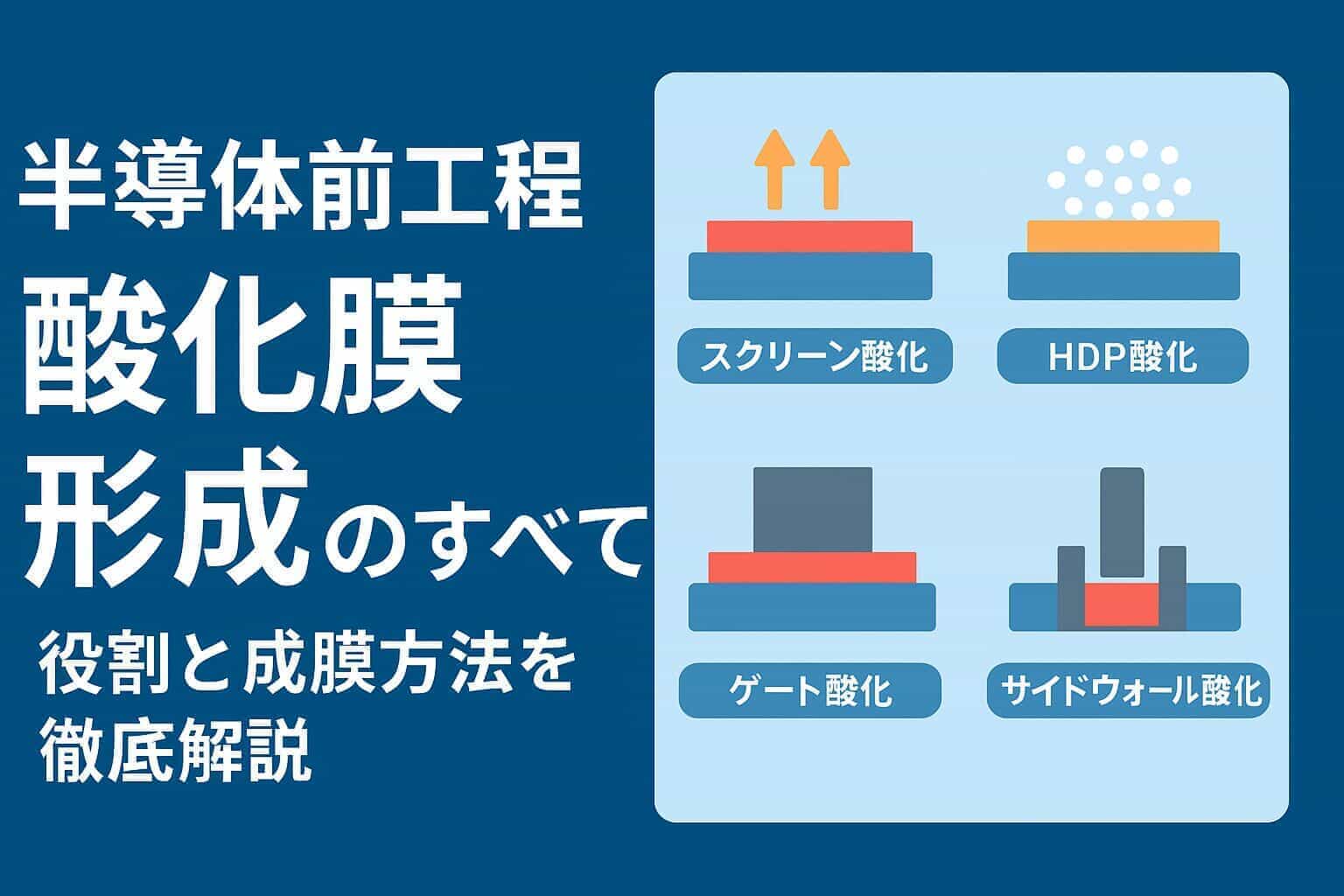

本記事は、半導体前工程の酸化膜形成について詳しく解説します。チップの保護、信頼性、電気特性に大きな影響を与える重要な工程です。一口に「酸化膜」と言っても、役割ごとに成膜方法や求められる特性が変わるため、各種類をイラストイメージ付きで説明します。

用語定義:

- 酸化膜: シリコン基板表面に形成されるSiO2層。絶縁・保護の役割を果たす。

- 半導体前工程: ウェーハ上に回路パターンを形成する工程(後工程は組立・テスト)。

想定読者

- 半導体前工程について詳しく知りたい方

- 酸化膜の役割について知りたい方

CMOSで使われる酸化膜形成の概要

今回は、主にCMOS(Complementary Metal-Oxide-Semiconductor)で使われる酸化膜形成について詳しく解説します。CMOSはCPUやDRAMなどのIC構造の基盤です。酸化膜は素子分離・絶縁に不可欠で、微細化が進む現代半導体で進化を続けています。

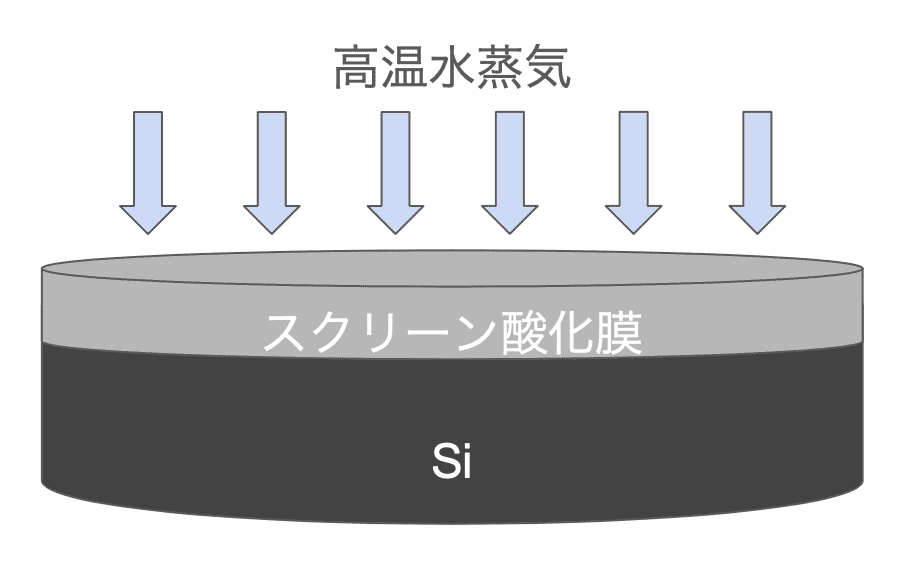

スクリーン酸化:イオン注入前の表面保護

スクリーン酸化は、イオン注入前に実施する酸化膜形成です。主に高温蒸気と反応させる熱酸化で実施します。酸化膜の厚さは数nm~数十nmです。

主な役割(箇点リスト):

表面保護: 注入時のダメージからシリコン表面を守る。

注入するイオンの深さ方向の制御: イオンが基板深部まで到達しすぎるのを防ぐ。

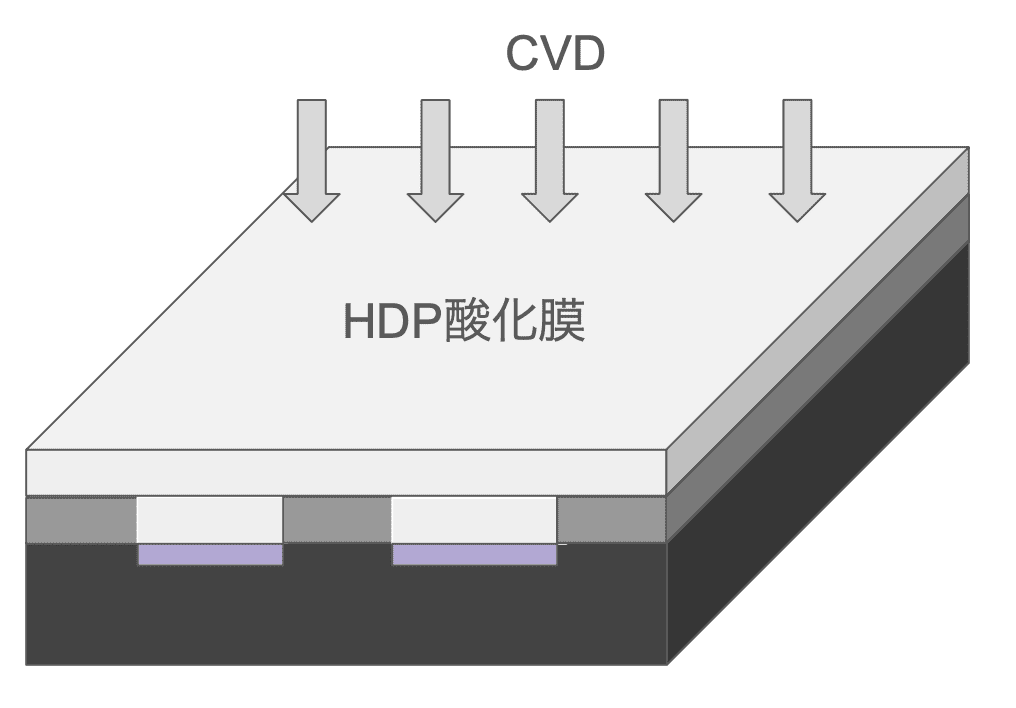

HDP酸化:素子分離のための高密度プラズマ蒸着

HDP(High Density Plasma)酸化は、**STI(Shallow Trench Isolation)**と呼ばれる主流の素子分離のために実施されます。基板を直接酸化せず、**CVD(Chemical Vapor Deposition)**で酸化膜を蒸着します。**CMP(Chemical Mechanical Polishing)**と組み合わせ、平坦化を実現。高平坦により露光時の焦点ずれを防ぎます。厚さは数百nm~数μm。

利点:

直接酸化より高速成膜可能。

トレンチ埋め込みが良好で、微細素子に適する。

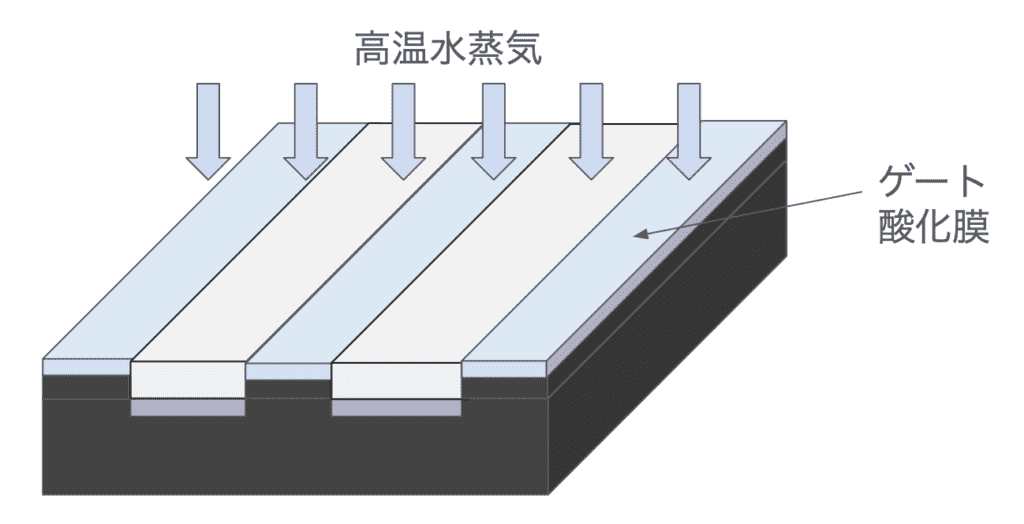

ゲート酸化:ゲート電極と素子の絶縁層

ゲート酸化は、ゲート電極と半導体素子間を絶縁するために実施します。STI形成とCMP完了後、露出したSiを熱酸化処理で酸化膜を形成。

微細化で厚さが薄くなるとリーク電流が増大するため、近年はHigh-k材料(例: HfO2)の蒸着で解決。物理的厚さを保ちつつ、誘電率を高めます。

課題と進化:

- リーク電流問題: 薄膜化の限界。

- 解決策: High-k材料の使用

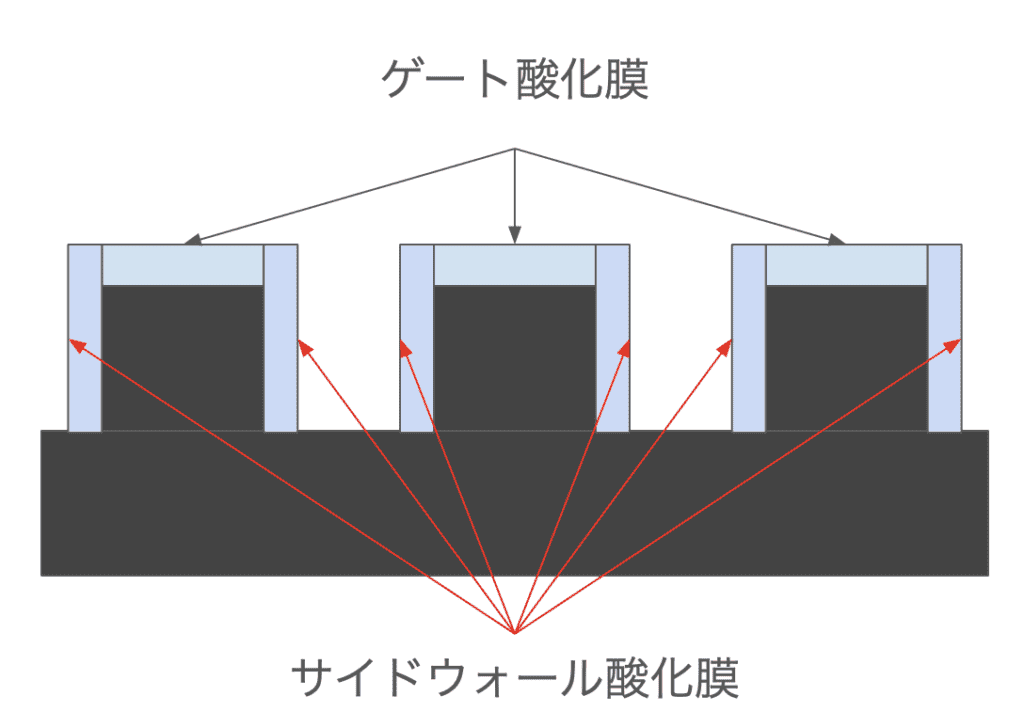

サイドウォール酸化:ホットキャリア劣化の抑制

サイドウォール酸化膜は、ホットキャリアの影響を抑制するために形成します。ホットキャリアとは、高いエネルギーを持った電子や正孔のことを指します。ホットキャリアがゲート酸化膜に注入されることで劣化に繋がります。ゲート酸化膜上にゲートを形成し、その後にサイドウォールの形成とイオン注入を行うことで、ホットキャリアの生成につながる電界を緩和します。サイドウォール酸化膜は、PVD(Physical Vavor Deposition)によって行います。

役割:

- イオン注入時のドーピング制御。

- ホットキャリア生成の電界緩和。

パッシベーション酸化膜:最終保護層

パッシベーション酸化膜は、素子化最後に形成する保護膜。外的環境(水・イオン・静電気)から守ります。厚さ数百nm~数十μmで、熱影響の小さいCVDやスパッタで形成。

利点: 高いバリア性能でチップの長期信頼性を確保。

まとめ:酸化膜は半導体製造の基盤技術

キーポイント:

| 酸化膜種類 | 主な役割 | 成膜方法 | 厚さ目安 |

|---|---|---|---|

| スクリーン酸化 | イオン注入制御・表面保護 | 熱酸化 | 数nm~数十nm |

| HDP酸化 | 素子分離(STI) | HDP-CVD | 数百nm~数μm |

| ゲート酸化 | ゲート絶縁 | 熱酸化/High-k ALD | 数nm |

| サイドウォール | ホットキャリア抑制 | PVD | 数十nm |

| パッシベーション | 最終保護 | CVD/スパッタ | 数百nm~数十μm |

以上、酸化膜の役割と成膜方法について解説しました。酸化膜は役割によって様々な種類があり、成膜方法も多岐にわたります。酸化膜がなければ現代の半導体は成り立たないと言える重要な技術です。

以上、酸化膜形成の役割と成膜方法を解説しました。役割ごとに多様な種類(熱酸化、HDP、High-kなど)があり、現代半導体なしでは成り立ちません。

次回の記事

次回の記事では、レジスト塗布や露光について解説します。

コメント