本記事の概要

本記事では、半導体パッケージ(後工程)の高集積化技術である、インターポーザについて解説します。前工程の微細化による高集積化の限界が見えてきた中で、今後の主流技術になると見られています。初心者にもわかりやすく解説していくので、ぜひ御覧ください。

想定読者

- 半導体の高性能化に向けた技術を知りたい方

- 半導体の技術トレンドをざっくり把握したい方

半導体の微細化の限界とインターポーザの台頭

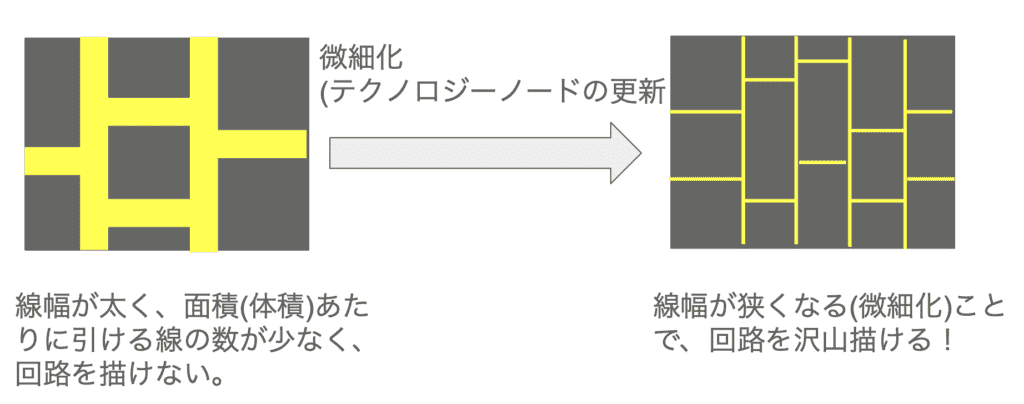

半導体はこれまで、いわゆる前工程における微細化で性能を上げてきました。微細化とは、

- 回路の幅を狭く

- 回路間の密度を高く

することです。微細化することによって

- 単位体積あたりに描ける回路の数が増える(高性能化)

- 同じ性能のチップをより小さくでき、ウェハーあたりの取れ高が増える(低コスト化)

- 回路を動作させるための電流を小さくできる(省電力化)

を実現できます。微細化は特にリソグラフィーの技術の進化によって進められてきました。現在実用化されているテクノロジーノードは2 nmプロセス(実際の線幅は20 nm)です。次世代のテクノロジーノードは1.4 nmであり、近年は微細化による高性能化が進みづらい状況にあります。

インターポーザとは?基本的な定義と役割

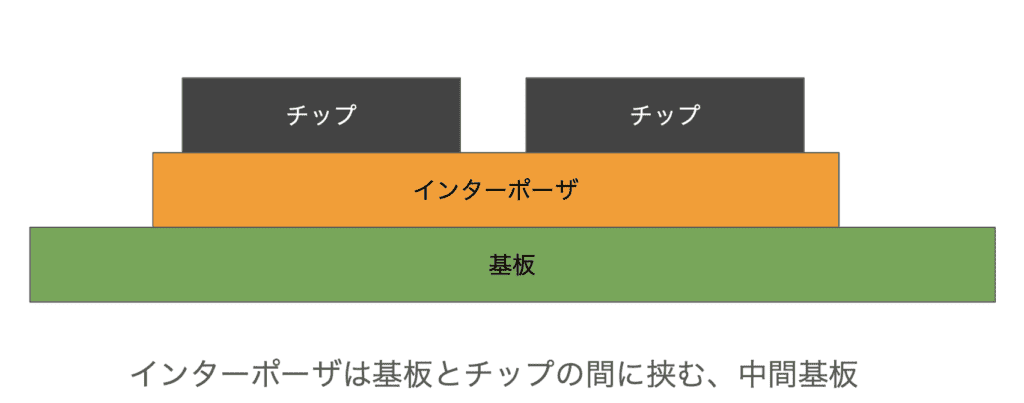

チップの微細化による高性能化が難しくなってきた中で、インターポーザを使った高集積化に注目が集まっています。インターポーザは、チップと基板の間に挟む、中間基板のことを指します。

インターポーザは、シリコン(Si)あるいは有機材料にRDL(再配線層)を形成することで、インターポーザーのチップ間あるいはチップ-基板間の最適な接続を実現します。

SoCからチップレット・SiPへの移行理由

では、なぜインターポーザが高集積化につながるのでしょうか?これは、昨今のSoCからチップレットとSiPへの移行と関係しています。

インターポーザは、チップを電気的に接続する機能を担っています。これまではいわゆるSoC(System on Chip)と言う形で、一つのチップに複数の機能を持たせていましたが、昨今はチップレットを用いた、SiP(System in Package)と言われる形に移行しつつあります。複数のチップ(チップレット)を組み合わせることで、パッケージとしてシステムを組むことをSiPといいます。チップレット化でチップ生産の複雑さや大きさを抑えることができ、チップの歩留まりを上げることができます。

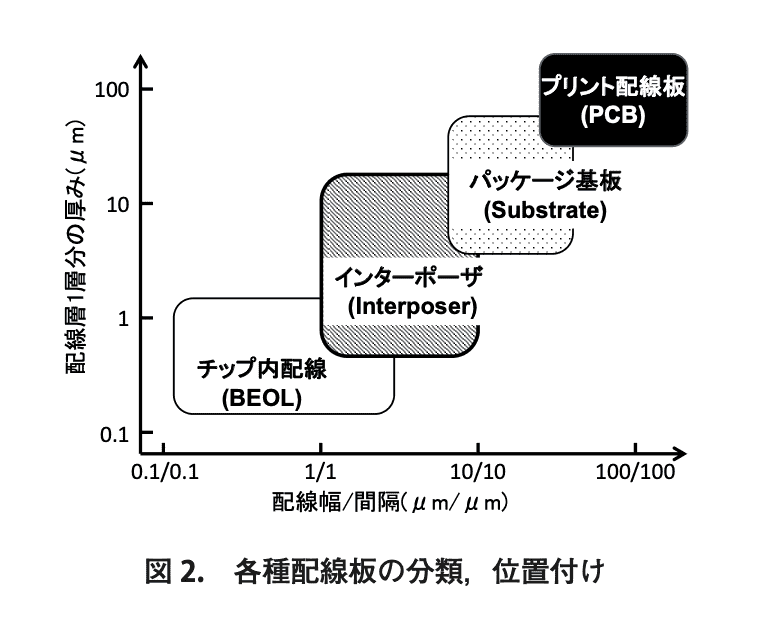

チップ同士を基板を介して接続すると、基板の細線幅が圧倒的に太いため、チップの性能を活かしきれません。現在主流のSiインターポーザーは、前工程の微細化技術を活用することで、チップと基板中間の細線幅を持ちます。そのため、基板に直接チップを接続するよりも効率的にパッケージを構築できます。

まとめ

今回はインターポーザの役割について、簡単に解説しました。インターポーザの主流はSiですが、近年はTSMCがCoWoS−Lと言われる、有機材料をベースにしたインターポーザの導入を進めています。また、SiPの大型化が進んでいる背景もあり、角形のパネルを使った生産技術の確率も進められています。今後、インターポーザが半導体の高性能化の主流になっていくため、ぜひ注目してください。

TSMC、”円から四角へ”の革命「CoPoS」を2029年量産へ:NVIDIAが最初の顧客、AI半導体のゲームを変える新戦略の全貌

コメント