- はじめに: 本記事の目的と対象読者

- 半導体前工程の主要プロセス

- インゴット(単結晶)成長:シリコンからSiCまで

- 円筒研削:インゴット形状の均一化

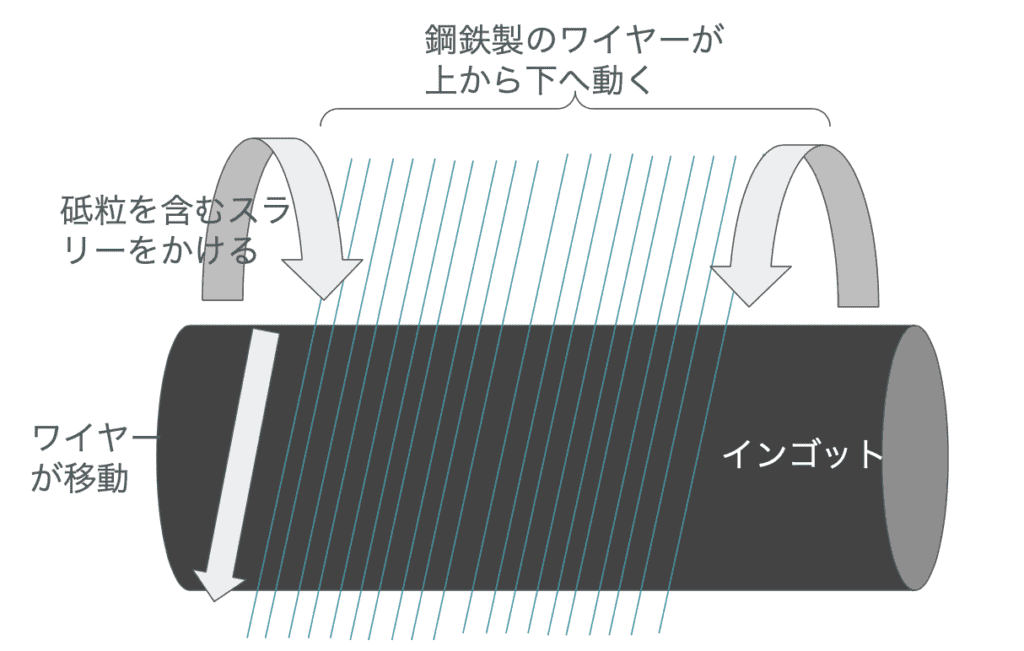

- 単結晶の切断(ウェハー化):マルチワイヤーソーからレーザースライスまで

- 端面研削(ベベリング):ウェハーの保護

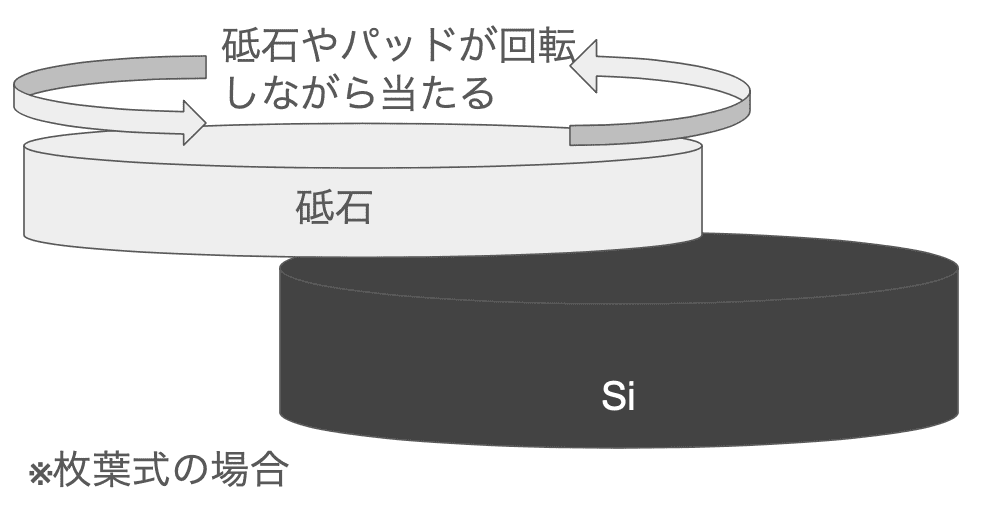

- 研削・研磨:ウェハーの厚さ調整と高平坦度の実現

- 洗浄・欠陥検査:コンタミ除去と品質確保

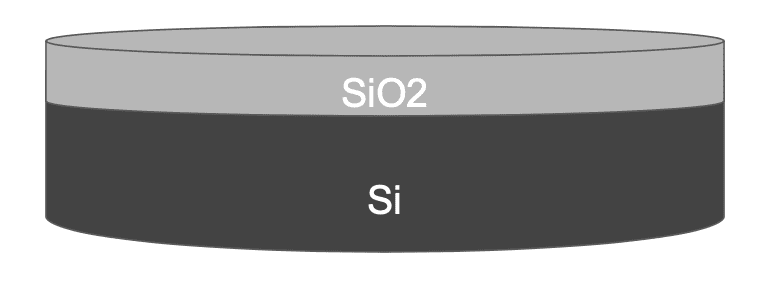

- ウェハー酸化(Si)またはエピ成膜(化合物半導体)

- レジスト塗布:回路形成の第一歩

- 露光:高精度な回路パターン転写

- 現像:ポジ型・ネガ型の違い

- エッチング

- レジスト除去

- イオン注入(Si):半導体の電気的特性付与

- 蒸着:PVDあるいはCVDによる薄膜形成

- CMP:化学反応と機械的な研磨の合わせ技で平坦化

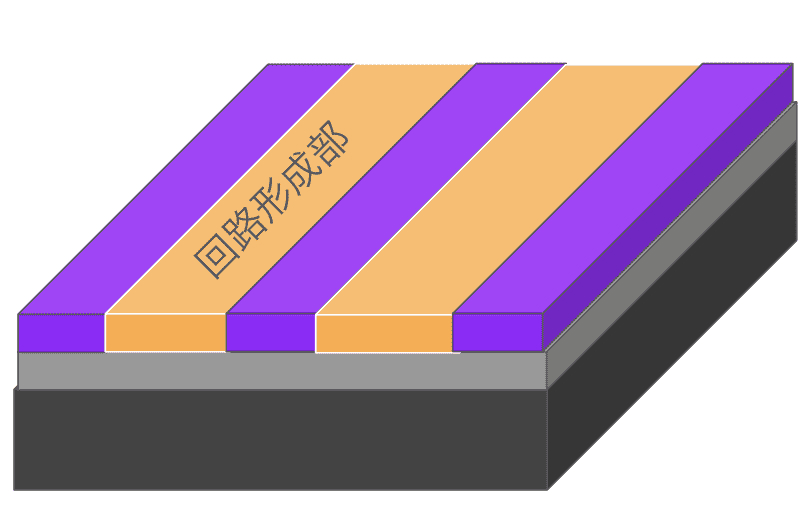

- レジスト塗布~CMPを繰り返し、回路形成

- 前工程の装置・素材が高収益な理由

- まとめ:前工程の魅力と課題

- 今後の予定:後工程解説とプロセス詳細

はじめに: 本記事の目的と対象読者

本記事の目的

本記事では、「半導体前工程」と呼ばれる工程について概要を説明します。また、EUVに代表される、前工程用の装置や素材の付加価値が高い理由についても解説します。

筆者は実際に半導体前工程のエンジニアとして働いていおり、可能な限り現場のエンジニアとしての視点も組み込んだ記事になるようにしています。

想定読者

- 半導体前工程について知りたい方

- 半導体前工程の各工程についてざっくり知りたい方

- シリコン以外の半導体の前工程についても知りたい方

- 半導体前工程の付加価値が高い理由を知りたい方

半導体前工程の主要プロセス

インゴット(単結晶)成長:シリコンからSiCまで

インゴット(単結晶)成長はその名の通り半導体単結晶を得るための工程です。インゴット成長の方法は複数あります。

- 溶融法・・・溶融させた原料から結晶を成長

- 昇華法・・・種結晶を上から吊るし、昇華させた原料を表面に堆積させる

- ガス法・・・種結晶に原料ガスを吹き付けて成長

などがあります。主流は溶融法で、SiCは昇華法が使われています。

溶融法の中でも手法が様々あります。

- チョクラルスキー法・・・種結晶を上から吊るし、溶融させた原料につけて徐々に引き上げる

- ブリッジマン法・・・多結晶の半導体を部分的に加熱し、温度勾配をつけることで狙いの単結晶を得る

- FZ法・・・多結晶の半導体棒を部分的に加熱し、溶融させた後に冷却することで単結晶を得る

- VGF法・・・種結晶を下に配置し、温度勾配を下から上につけることで結晶を得る

SiやInP、GaP、GaAsはチョクラルスキー法、GaAsはVGF法やブリッジマン法も使われています。(※2025年8月30日修正)

円筒研削:インゴット形状の均一化

各種結晶成長で得られた単結晶は、外径が不均一になっています。また、外周部は多結晶となっていることもあるので、円筒研削を行うことで外径を均一にします。長尺の結晶の場合は、先に結晶の切断を行ってから円筒研削を行うこともあります。

単結晶の切断(ウェハー化):マルチワイヤーソーからレーザースライスまで

単結晶を切断することでウェハーを得ます。通常はマルチワイヤーソーと言われる、均一な間隔に並んで高速移動する鋼線の上に砥粒をかけ流して切断する装置を用います。鋼線に砥粒が付着しているタイプのマルチワイヤーソーも存在します。

SiCのような、難加工性の素材はマルチワイヤーソーで切断すると断線のトラブルや加工に長時間かかるなど課題があります。そのため、レーザースライスという技術が一部実用化されています。これは単結晶にレーザーを照射し、単結晶内部の狙った位置に焦点を絞ることでアブレーション(熱的な分解)を起こし、ウェハーを剥離する技術です。

端面研削(ベベリング):ウェハーの保護

ウェハーの端面を整えるのがべべリングの役割です。端面の形状を整えることで、割れや欠けを抑制できます。溝の掘られた回転する砥石にウェハー端面を押し付けて加工を行います。

研削・研磨:ウェハーの厚さ調整と高平坦度の実現

切断後のウェハーは非常に平坦度が悪く、また、厚さも不均一になっています。ウェハーの厚さを揃え、平坦度の要求を満たすように加工するのが研削と研磨の工程です。

洗浄・欠陥検査:コンタミ除去と品質確保

研削と研磨を終えたウェハーは研磨くずやスラリーで汚染されているため、洗浄を行います。先生は各社工夫しており、洗剤やIPAなどの溶剤、超音波を組み合わせて可能な限りコンタミを除去しています。

洗浄後は基板の検査を行い、欠陥や形状が規格内に収まっていることを評価します。

ウェハー酸化(Si)またはエピ成膜(化合物半導体)

ウェハー酸化は、ウェハーの表面に酸化膜(SiO2)を形成する工程です。SiO2は保護膜として作用します。SiO2はSi上に形成した回路間を絶縁し、故障を防ぎます。後の工程であるエッチングやイオン注入でも保護膜として機能し、目的の回路形成を助けます。

一方、SiCやGaN、GaAsなどの化合物半導体ではウェハー酸化の工程はありません。代わりにエピ工程という機能性膜の形成を行います。これは、Siのプロセスではイオン注入に類似したプロセスです。

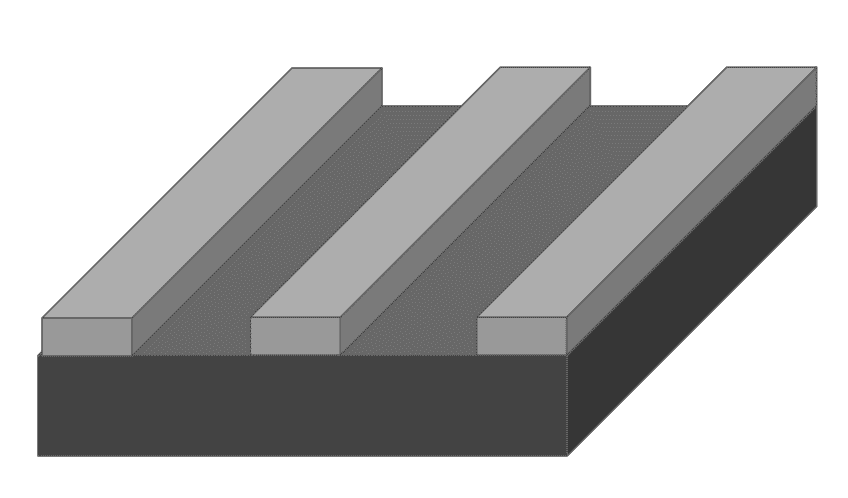

レジスト塗布:回路形成の第一歩

酸化膜の形成後は、ウェハー表面にレジストを塗布します。レジストは回路を露光するために必要です。レジストがあることで、露光によって回路を掘ること出来るイメージです。

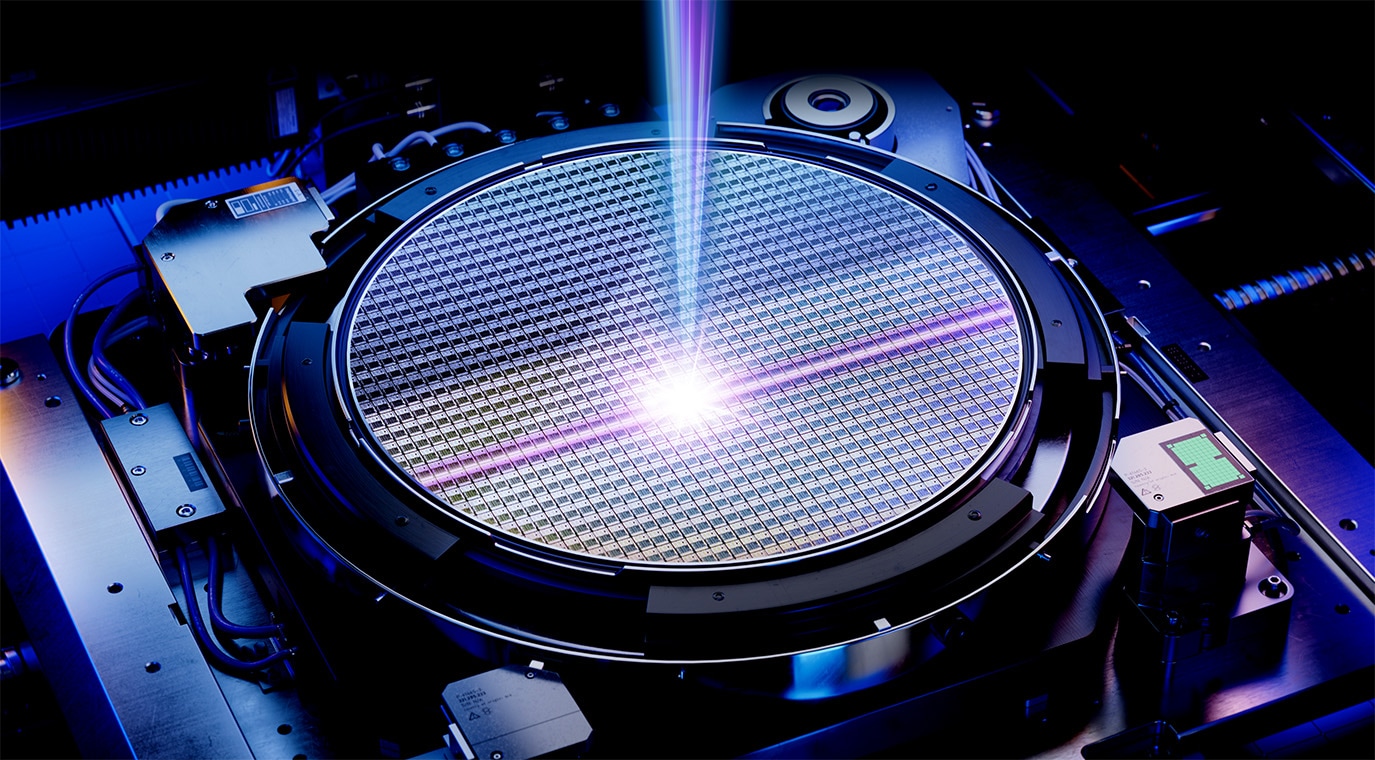

露光:高精度な回路パターン転写

露光はレジスト上に回路パターンを転写する工程です。大きなフィルムに描かれた回路のパターンを、レンズを使ってチップサイズまで縮小し、レジスト上に焼き付けます。世代を追うごとに回路は細く複雑になるため、露光装置への光学・機械精度要求も上がります。

現像:ポジ型・ネガ型の違い

レジストの焼き付けた部分(あるいは焼き付けられなかった部分)を除去する工程を現像といいます。現像によって回路部分が露出します。焼き付けられた部分を除去する場合は「ポジ型」、焼き付けられなかった部分を除去する場合は「ネガ型」と言います。

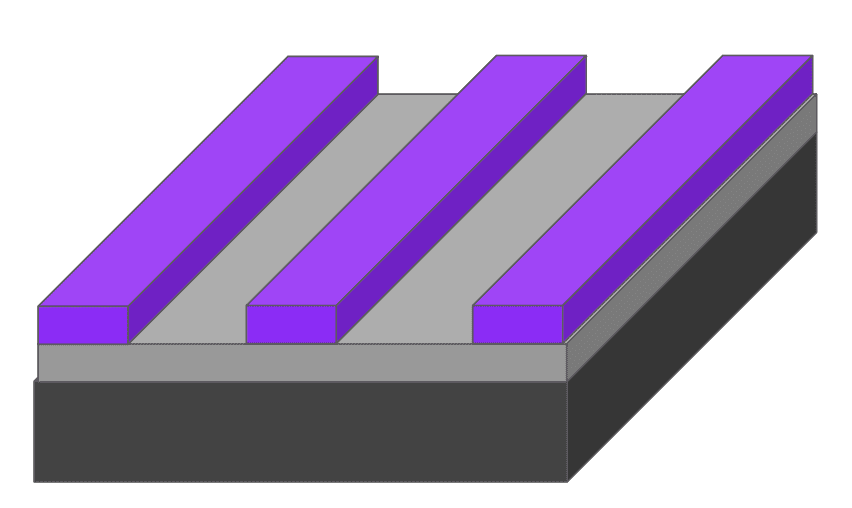

エッチング

エッチングは、現像で露出したウェハーの酸化膜(あるいはエピ膜)を除去する工程がエッチングです。Siのエッチングは、表面のSiO2を除去するため、HF(フッ酸)ガスを使用します。ガスやプラズマを使う場合は「ドライエッチング」といいます。一方、GaNやGaAsは薬液を使ってエッチングするため、これを「ウェットエッチング」と呼びます。

レジスト除去

エッチングによって回路を彫り込んだら、レジストの役割は終了するため、除去します。レジストは薬液を使って除去するウェットタイプと、オゾン酸化やプラズマを使ったドライタイプがあります。

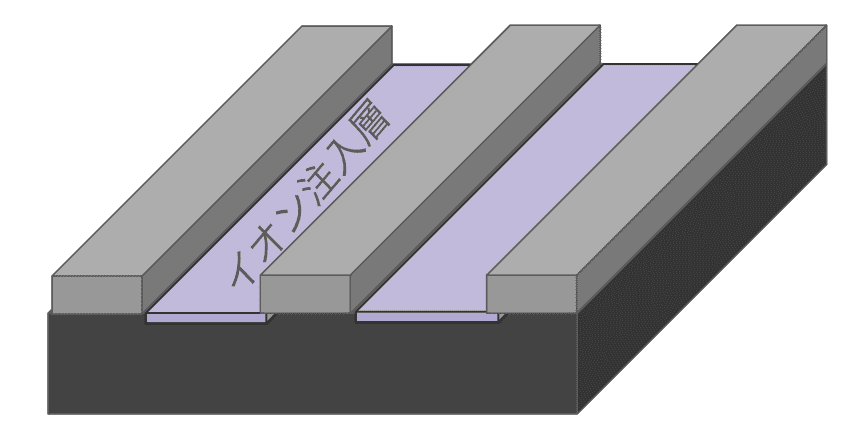

イオン注入(Si):半導体の電気的特性付与

シリコンの場合は、レジストを剥離した後にイオン注入を行います。イオン注入によって、絶縁体に近い状態のシリコンが、電気的な特性を持つ半導体になります。イオン化した元素を電圧を欠けて加速させ、シリコンに打ち込みます。

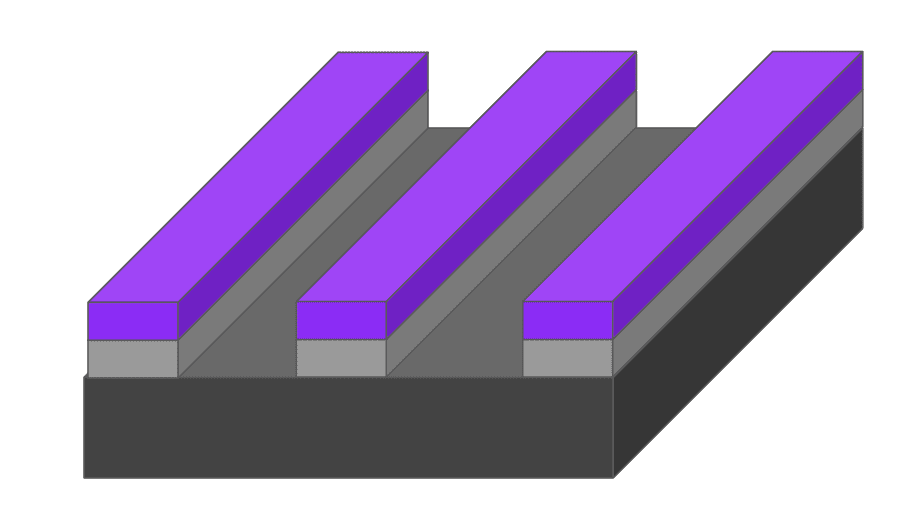

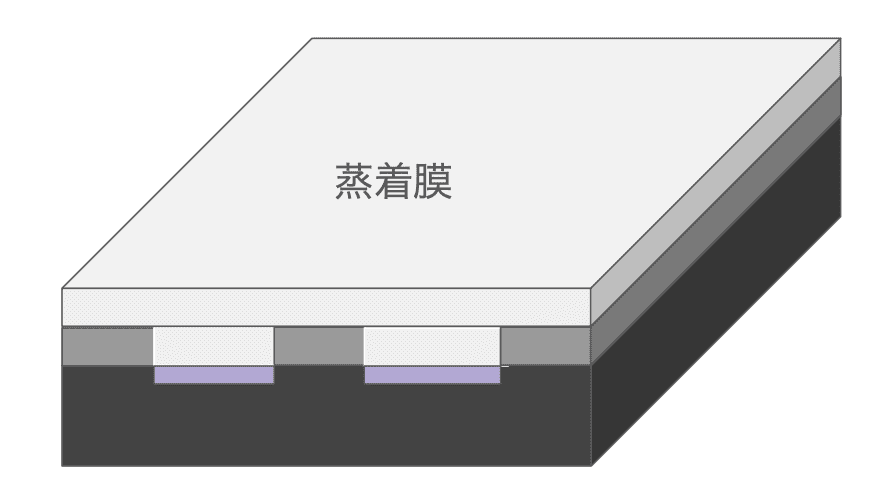

蒸着:PVDあるいはCVDによる薄膜形成

彫り込んだ回路の保護や絶縁、接続などを目的として、薄膜の蒸着を行います。蒸着によって形成される薄膜の厚さは、オングストローム単位から数百μm程度まで様々です。蒸着は金属などのターゲットにプラズマをぶつけて蒸着させるPVD(Phisycal Vapor Deposition、物理蒸着法)と、原料ガスや微粒子を吹き込んで半導体表面で目的の物質を作るCVD(Chemical Vapor Deposition、化学蒸着法)に分けられます。

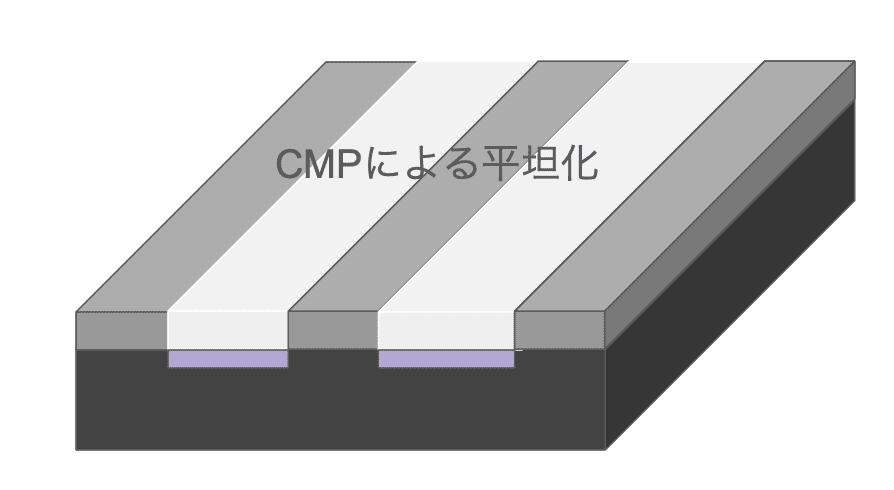

CMP:化学反応と機械的な研磨の合わせ技で平坦化

CMPはChemical Mechanical Polishing、すなわち化学反応を使いながら機械的に研磨を行う工程です。CMPによってウェハー表面を平坦化し、複雑な回路を精密に形成することが可能となります。

ここまでの工程で出来上がった回路パターンは、ところどころ膜厚が不均一になっています。CMPを行わずに以降の工程を行うと、出来上がったチップの厚さも不均一になり、所望の特性を得られなくなります。

レジスト塗布~CMPを繰り返し、回路形成

CMP後はレジスト塗布に戻り、CMPまでを繰り返し行うことで目的の回路の形成を行います。

前工程の装置・素材が高収益な理由

最後に、前工程の装置や材料の付加価値が高い理由を紹介します。露光装置の最新型は390億円/台ともいわれており、非常に高額になっています。レジストのリーディングカンパニーである東京応化の2024年の営業利益率は17%にもなり、化学メーカーとしては驚異的です。

詳細は以下の文献を参照いただきたいのですが、前工程の付加価値の理由は、「ウェハーという巨大な板に何万個もの付加価値の高いチップを作っているから」です。前工程は、ウェハー自体の付加価値を上げていく工程になるため、元値が数万円/枚のウェハーが、最終的に数百万円/枚まで価値が上がります。そして、年間で何万枚もその高付加価値のウェハーを生産することになります。そのため、390億円の露光装置を購入しても、すぐに投資額を回収できるのです。

一方、後工程は、ウェハーから切り取ったチップの付加価値を上げる工程になってしまうため、チップ単価の絶対額が低いことから前工程よりも付加価値(=収益性)が上がりません。

https://www.tok.co.jp/application/files/6317/4314/5605/securities_2412.pdf

まとめ:前工程の魅力と課題

以上、半導体前工程の概要と付加価値の高さの理由について紹介しました。前工程は付加価値が高いものの非常に大きな投資を継続して行う必要があります。そのため、いわゆるシリコンサイクルの底に向かっているときは、投資を回収できず損益の額が大きくなりすくもあります。

赤字でも投資ができる財務的な体力が必要なため、また、技術面でのハードルも年々上がっていることもあり、ロジック半導体製造のプレイヤーはTSMC、IntelそしてSamsungの3社まで絞られました。

今後の予定:後工程解説とプロセス詳細

今後は、半導体後工程に関する解説や、前工程に含まれる各プロセスの詳細についても解説していきます。楽しみにお待ちください!

半導体材料の紹介記事は以下です。こちらもぜひご一読ください!

コメント