はじめに:なぜ今、半導体パッケージ技術が注目されるのか?

この記事でわかること

- シリコン、有機、ガラスインターポーザなど最新技術のトレンド

- SoCの微細化と歩留まりの問題

- SiP(System in Package)とチップレット技術のメリッ

本記事では、年々重要度が増す「半導体パッケージ技術」が注目される理由について解説します。 これまでの技術進化の中心は「前工程での微細化」でしたが、物理的な限界やコストの増大により、「後工程(パッケージング)」で性能を向上させるアプローチへの要求が急激に高まっています。

想定読者

- 先端半導体に興味を持った初学者

- パッケージ技術のトレンドを知りたい方

1. 微細化の限界:なぜパッケージ技術が重要視され始めたのか?

SoC(System on Chip)の進化と「歩留まり」の壁

半導体は、過去から基板上(マザーボード or ビルドアップ基板)に実装され、チップ間の接続を行ってきました。基板の微細化はチップよりも困難であったため、基板を介したチップ間の通信は速度が遅く、高性能化したチップの性能を活かしきれなくなりました。

そこで、1つのチップに複数の機能をもたせる、SoC(System on Chip)が発達しました。SoCは、

- チップ内で通信が完結するため、十分高速でチップの性能を活かしきることができる

- チップ内に複数機能を集積するため、小型化が可能

2010年代のスマートフォンの普及と高性能化の流れにより、小型で高機能なチップの需要が急速に伸びたため、SoCが発展しました。

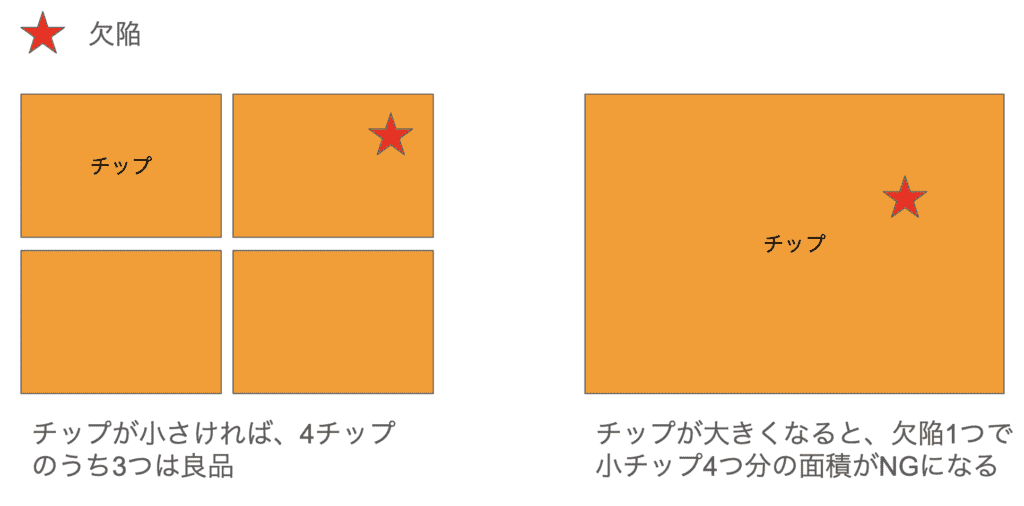

しかし、高性能化・機能の増加により、チップサイズが大型化が避けられなくなりました。微細化による高性能化とチップの巨大化が同時に進むことで、歩留まりの深刻な低下が問題になりました。

実際の製造現場における大チップ化の弊害

私自身も大チップを使った製品の歩留まり管理に苦労した経験があります。

例えば、ウェハーサイズを一定にすると、350 mm角のチップであれば、1インチあたりの取れ高は15000個程度になります。一方、1000 mm角のチップになると、ダイシングのロスや外周部のロスにより、1500個程度しか取得できません。サイズは8倍程度しか変わりませんが、取れ高は10倍です。

1000 mm角のチップと350 mm角のチップでは、1個のチップが歩留まりに与える影響が、なんと10倍違うことになります。そのため、より厳密な品質管理が求められる様になるのです。私が扱っている製品では、実際350 mm角のチップと1000 mm角のチップで、歩留まりが10%以上違い、非常に問題になっていました。

困難を極めた品質管理を改善した経験は、過去記事にまとめています。ぜひご一読ください。

次世代半導体製造の鍵を握る「チップレット」とは – Rapidus

2. ゲームチェンジャー:SiPとチップレット技術

そこで急速に重要度が増した技術が、

- SiP(System in Package)

- インターポーザ

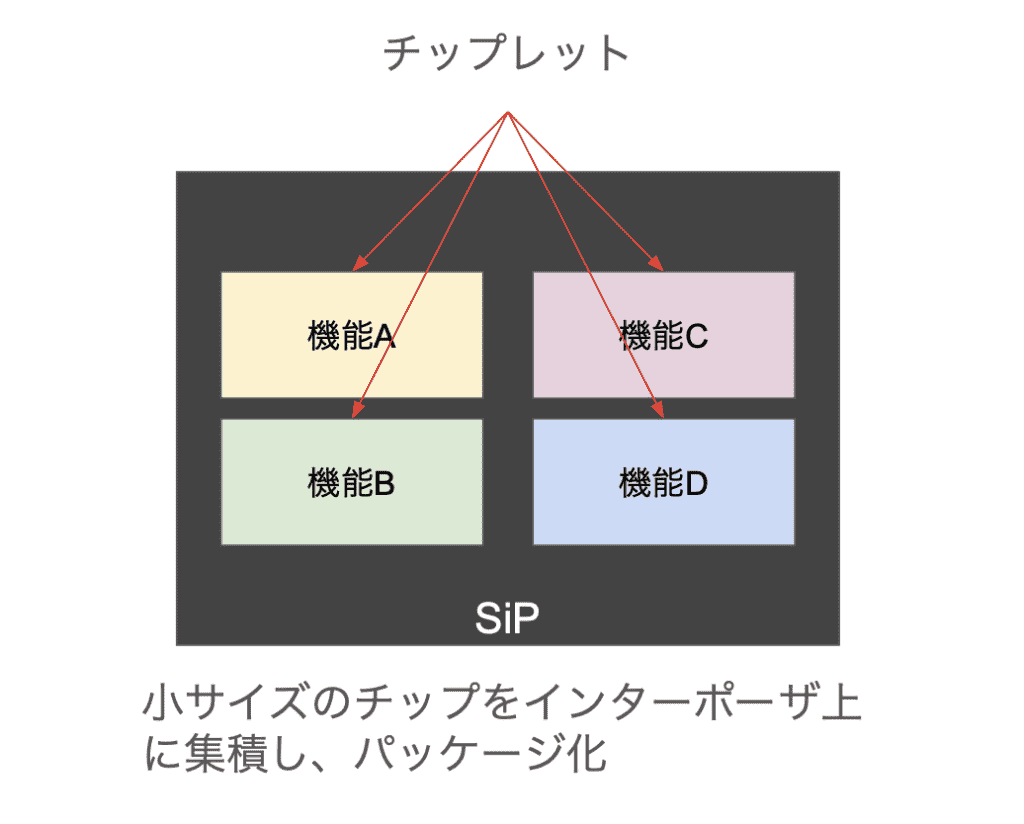

です。SiPは、機能を単純化したチップ(チップレット)を組み合わせてパッケージ化し、あたかも一つのチップのように扱う技術です。チップレット化することで、SoCのような巨大で複雑なチップを製造する必要がなく、微細化しても歩留まりの低下を抑えられるメリットがあります。

SiPの概念は過去からありましたが、前述した通り、基板側の微細化が追いついていなかったため、SoCが主流になりました。しかし、インターポーザの登場で状況が変わりました。

インターポーザの役割とシリコン(Si)の課題

インターポーザは基板とチップの間に挟まる、中間基板です。現状主流のSiインターポーザは、素材がSiのため、前工程と同様の技術を使って微細化が可能です。そのため、Siインターポーザを介してチップレット間の接続を行えば、これまでネックであった速度の遅延をある程度解消可能です。

しかし、Siインターポーザにも欠点があります。

- Siの自体や加工のコスト

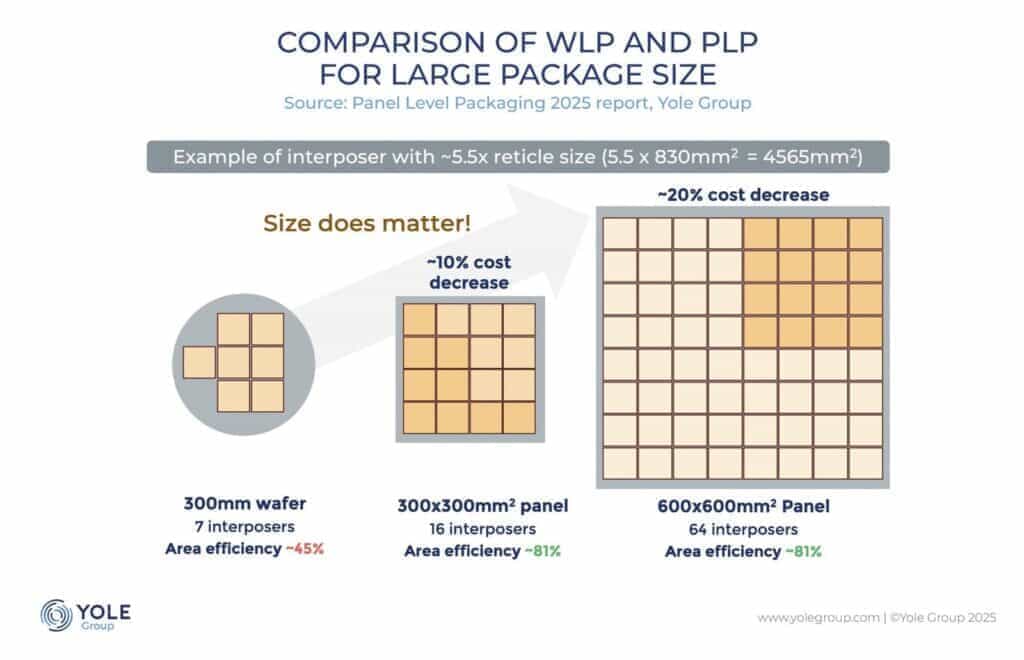

- Siのウェハーサイズの制約による取れ高の少なさ

特に、ウェハーサイズで取れ高が制限される点が生産コストを押し上げるため、問題視されています。ウェハー丸いため、角形であるインターポーザを取得するには効率の悪い形状です。SiPの機能を拡充させるには、自ずと搭載するチップレットを増やす必要があります。その結果、パッケージが巨大化し、インターポーザもより大きなものが求められており、伴ってウェハーから取得できるインターポーザの取れ高が悪くなります。

ウェハーでは面積あたりのインターポーザーの取れ高が少ない

ウェハーのサイズも12インチ以降大型化の流れは止まっており、より大サイズのものを求めればウェハーのコストが嵩みます。

有 機 イ ン タ ー ポ ー ザ に よ る 異 種 デ バ イ ス の シ ス テ ム イ ン テ グ レ ー シ ョ ン

Is Panel-Level Packaging (PLP) finally emerging? – Yole Group

JOINT3設立のご紹介 – 株式会社レゾナック・ホールディングス

3. 次世代の主役:有機・ガラス・パネルレベルパッケージ(PLP)

Siインターポーザのコストがかさみつつある中、Siに代わり有機材料やガラスコア材を使ったものが実用化されつつあります。前工程の技術を直接的に活用できないデメリットはあるものの

- Siに比べて低コスト

- 大型化と角形への形成が可能

という大きなメリットがあります。特に、大型化と角形形成が可能な点が大きなメリットであり、角形(パネル型)に成形すれば、インターポーザの製造コストを劇的に下げる事ができます。

TSMCの最先端パッケージ戦略:ロジックとHBMをパッケージ化するCoWoSとSoIC

前工程を担うFabの代表格であるTSMCは、直近はパッケージ技術の開発にも力を入れています。ヘテロジニアス・インテグレーション(異種チップ集積)を目指し、各種技術の開発・導入を進めています。

現在はロジックチップとHBM(最新はHBM4)をパッケージ化する技術の導入を推進していて、Siインターポーザーからコストメリットの大きな有機インターポーザーにシフトしようとしています。

有機インターポーザではCoWoS−RやCoWoS−Lと呼んでいる技術の採用を進めています。

- CoWoS-R・・・有機インターポーザ

- CoWoS−L・・・有機インターポーザ+ブリッジチップのハイブリッド

RはRDL(Redistribution Layer、再配線)のR,Lは「Local Silicon Interconnect」のLです。CoWoS−Lでは、埋め込んだチップを介することで、Siインターポーザと同様の微細化した配線でチップ間の接続が可能になります。

パネルレベルでは、2027年には310×310サイズのパイロット生産、2029年にCoPoSと言う呼称で本格的な生産ラインを立ち上げる計画を出しています。

また、TSV(Through Silicon Via)を使ってチップを縦に積む、いわゆるハイブリッドボンディングを使った3Dパッケージの開発も進めており、こちらはSoICと呼んでいます。

Is Panel-Level Packaging (PLP) finally emerging? – Yole Group

パッケージ技術の重要度が増す中、素材屋はどう戦うか?

SoCからSiP、インターポーザ、そしてパネルと次々に新しいパッケージ技術が発達する中、材料メーカーはどう戦うべきか?非常に難しい問題になりつつあります。

- 技術の大きな方向性は顧客が決める

- 有力な顧客は今後10年で1~2社に絞られる

- 顧客の顧客(=ファブレスとハイパースケーラー)が独自設計したパッケージを要求する

- 省電力要求が高まる

ことを考えれば

- ハイパースケーラー(GAFAM等)との直接連携: チップの最終仕様を決める顧客へのスペック提案。

- 光電融合技術への投資: 銅配線の限界を超える、次世代の通信技術(IOWN構想等)への参入。

- エコシステムの形成: 巨大な設備投資に耐えうる企業規模への拡大や、ファブやOSATとの強固なパートナーシップ。

などが考えられます。

具体的には、ファブやOSATとのコミュニケーション強化のため、開発部隊を顧客の工場近隣に設置することも視野に入れるべきと考えています。可能であれば、現地生産まで実施できる体制を整え、「顧客の要求に素早く的確に応えられるメーカー」としての信頼を醸成する方向性を打ち出すなど。

一方、開発や生産拠点の増設に投じる資金力に制限がある企業が多数あるのも事実です。そのため、材料メーカーにも統廃合あるいは巨大資本による市場の寡占が進むと見られます。

まとめ: 今後はパッケージが半導体の主役になりうる

以上、半導体パッケージ技術の動向について解説しました。今後ますます重要性が増す技術であり、装置、材料含め複数の企業がビジネスチャンスを伺っています。激しい変化と共創にさらされること必至なため、革新的な技術が生まれる可能性もあります。ぜひ注目してください。

インターポーザーの詳細については、下の解説記事にまとめています。ぜひご一読ください。

コメント